Principles of Pipelining

Here we look at the notion of pipelining, a technique that has done so much to improve the performance of computers without requiring significant changes in the underlying technology; that is, it does not rely on faster clocking of faster devices.

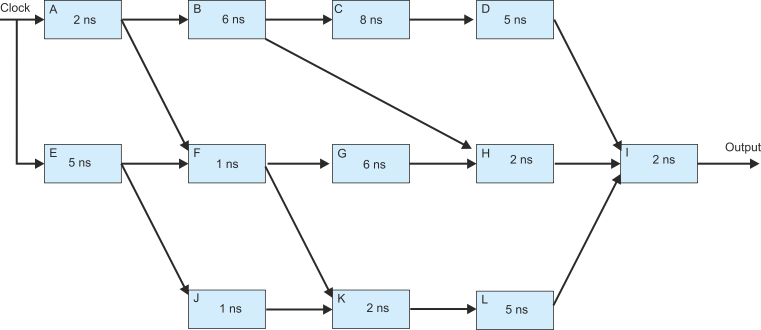

Consider the system below that consists of a network of interconnected building blocks

or circuits. Each block is labeled A to L and has an input-

If you consider the top row of blocks A, B, C, and D, the delay of a signal through the circuit is 2 + 6 + 8 +5 = 21 ns. This means that the output from block D will not be valid until at least 21 ns have elapsed since block A was clocked.

How long does it take for the output to become valid?